## AUTOVM: ACCELERATING CONVOLUTIONAL NEURAL NETWORK TRAINING WITH ACTIVELY MANAGED GPU VIRTUAL MEMORY

by

Luyuan Chen

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

#### Abstract

# AutoVM: Accelerating convolutional neural network training with actively managed GPU virtual memory

Luyuan Chen

Master of Applied Science

Graduate Department of Electrical and Computer Engineering

University of Toronto

2020

The size of neural networks a GPU can train is limited by the GPU's memory capacity. Although GPU virtual memory enables training arbitrarily large neural networks, such trainings are often accompanied by severe performance penalties. Furthermore, popular frameworks for constructing machine learning applications, like TensorFlow, have disabled using GPU virtual memory by default. We propose AutoVM, a software layer that can better manage GPU virtual memory in neural network training by incorporating our understandings of neural networks. AutoVM schedules data transfers between GPU and CPU memory to relieve the memory pressure on GPU; and in turn optimizes training speed. We have integrated AutoVM into TensorFlow such that existing machine learning applications can benefit from AutoVM with minimal effort. Our tests suggest that training VGG-19 using AutoVM can be at most 2.5× faster compared to using default Nvidia virtual memory.

## Contents

| 1 | Intr | roduct | ion                       | 1  |

|---|------|--------|---------------------------|----|

|   | 1.1  | Motiv  | ating example             | 3  |

|   | 1.2  | Contr  | ibutions                  | 4  |

|   | 1.3  | Outlin | ne of the Dissertation    | 4  |

| 2 | Bac  | kgrou  | $\mathbf{nd}$             | 5  |

|   | 2.1  | GPUs   |                           | 5  |

|   |      | 2.1.1  | Hardware architecture     | 7  |

|   |      | 2.1.2  | Programming model         | 11 |

|   |      | 2.1.3  | Memory management         | 14 |

|   |      | 2.1.4  | GPU performance issues    | 16 |

|   |      | 2.1.5  | Accelerated libraries     | 17 |

|   | 2.2  | Deep   | neural network            | 17 |

|   |      | 2.2.1  | Layers in neural networks | 19 |

|   |      | 2.2.2  | Inference and Training    | 22 |

|   |      | 2.2.3  | Gradient descent          | 23 |

|   |      | 2.2.4  | Workload in CNN training  | 28 |

|   | 2.3 | Tensor  | Flow                                         | 28 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.3.1   | Programming and execution model              | 29 |

|   |     | 2.3.2   | Computation graph                            | 31 |

|   |     | 2.3.3   | Execution order                              | 31 |

|   |     | 2.3.4   | GPU support                                  | 32 |

| 3 | Des | ign     |                                              | 33 |

|   | 3.1 | Motiva  | ation and Problem Statement                  | 34 |

|   | 3.2 | Design  | o Overview                                   | 36 |

|   | 3.3 | Policy  |                                              | 37 |

|   |     | 3.3.1   | Identifying tensors to move                  | 37 |

|   |     | 3.3.2   | Identifying when to transfer tensors         | 40 |

|   | 3.4 | The m   | nechanism                                    | 45 |

|   | 3.5 | Limita  | ations                                       | 46 |

| 4 | Rev | verse e | ngineering Nvidia virtual memory             | 48 |

|   | 4.1 | cudal   | MemPrefetchAsync() v.s. cudaMemAdvise()      | 49 |

|   |     | 4.1.1   | Method                                       | 50 |

|   |     | 4.1.2   | Findings                                     | 51 |

|   | 4.2 | Efficie | nt memory transfer between devices           | 51 |

|   |     | 4.2.1   | Overlapping memory transfer with computation | 51 |

|   |     | 4.2.2   | Alternating the launch order                 | 53 |

|   |     | 4.2.3   | Avoiding page faults                         | 54 |

|   |     | 4.2.4   | AutoVM and pre-access                        | 55 |

|   | 4.3 | Throughput of cudaMemPrefetchAsync() transfers           | 57        |

|---|-----|----------------------------------------------------------|-----------|

| 5 | Imp | blementation                                             | <b>58</b> |

|   | 5.1 | Overview                                                 | 58        |

|   | 5.2 | The policy                                               | 60        |

|   |     | 5.2.1 Integrating AutoVM                                 | 61        |

|   | 5.3 | The mechanism MemOp()                                    | 62        |

|   |     | 5.3.1 Adding support for cudaMemPrefetchAsync()          | 63        |

|   |     | 5.3.2 Accessing cudaMemPrefetchAsync() from an operation | 63        |

|   | 5.4 | Supporting pre-access                                    | 64        |

| 6 | Exp | periment                                                 | 65        |

|   | 6.1 | Environment setup                                        | 65        |

|   | 6.2 | Experiment design                                        | 65        |

|   |     | 6.2.1 Experiment code                                    | 66        |

|   |     | 6.2.2 Test cases                                         | 67        |

|   |     | 6.2.3 Data collection methods                            | 69        |

|   | 6.3 | Results                                                  | 70        |

|   |     | 6.3.1 AlexNet                                            | 70        |

|   |     | 6.3.2 VGG-19                                             | 74        |

|   |     | 6.3.3 ResNet-152                                         | 75        |

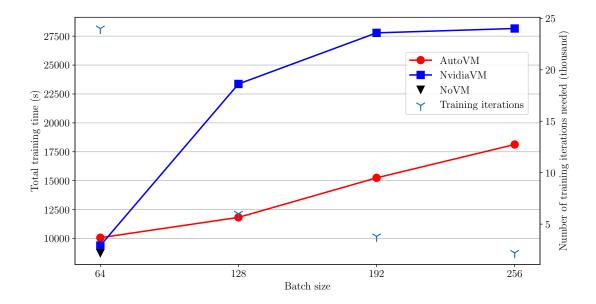

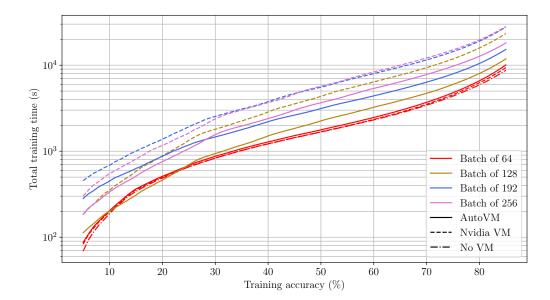

|   |     | 6.3.4 Full Training Run Experiment                       | 76        |

|   |     | 6.3.5 Summary of results                                 | 78        |

|   | 6.4 | Discussion                                               | 70        |

|    | 6.5    | Future   | improvements              | 79 |

|----|--------|----------|---------------------------|----|

|    |        | 6.5.1    | Further optimizing AutoVM | 80 |

| 7  | Rela   | ated w   | ork                       | 82 |

| 8  | Con    | ıclusioı | n                         | 85 |

| Bi | ibliog | graphy   |                           | 86 |

## Chapter 1

### Introduction

GPUs have played a major role in catapulting machine learning from largely theoretical concepts to practical solutions capable of solving a variety of non-trivial problems. Machine learning computations are dominated by matrix and vector operations that can only be executed relatively slowly on traditional CPUs. Meanwhile, GPUs were initially designed and optimized for graphical processing, which also primarily involves matrix operations. Thousands of simple processing units within GPUs allow parallel computation of such matrix and vector operations and thus execute such operations far more quickly than CPUs. Because of the similarity of computations between graphics processing and machine learning, and the speed at which they can execute these computations, GPUs have become the dominate infrastructure for machine learning.

GPUs are CPU-controlled co-processors that have their own memory system, called *global memory*, which is optimized for highly-parallel access from their compute cores. DMA (direct memory access) engines on the GPU are responsible for transferring data between CPU and global memory over a PCI-Express (or NVLink) interconnect. One key issue for many computationally intensive application running on GPUs is the fact that the size of GPU memory is fixed and typically much smaller than CPU memory (referred to as *host memory* in GPU terms) sizes.

In this dissertation, we identify methods to manage global memory to support running GPU applications efficiently with memory requirements larger than what is physically available on the GPU. We specifically target convolutional neural networks (CNNs) that have been successfully applied to numerous applications, including image classification, video analysis, and action recognition [25]. Over the last

decade, CNNs have been growing deeper with more layers and thus higher demands for compute and memory resources. For example, the winner of 2012 ImageNet Large-Scale Visual Recognition Challenge (ILSVRC), AlexNet [13], had 5 convolution layers and 2 dense layers. The winner of the 2015 contest, ResNet-152 [7], had over 150 convolution layers. The amount of available memory on GPUs, on the other hand, has not grown as fast as CNN memory requirements. For example, Google's *inception v4* [22] model has 515 layers, consuming over 80GB of global memory during training with 64-image batches. To date, no commercially available one-GPU setup has enough GPU memory to train this network. Consequently, these kinds of networks can only be trained by using expensive multi-GPU setups.

Modern Nvidia GPUs support virtual memory and paging. Virtual memory support allows applications to run even if they use more memory than what is physically available. Despite the convenience provided by virtual memory, the default GPU virtual memory management policy is unaware of the workload being processed on the GPU. As a result, GPU virtual memory is managed in a suboptimal way with an attendant performance penalty.

Our work explores efficient GPU virtual memory management for CNNs. In particular, we propose AutoVM that smartly manages the GPU virtual memory in CNN training. AutoVM is a software layer that manages GPU virtual memory actively and transparently to the CNN application. Specifically, AutoVM offloads tensors without immediate reuse to host memory, and prefetches offloaded tensors back to global memory prior to their consumptions.

The computations in CNNs are often represented by a data flow graph (computation graph) in machine learning frameworks like TensorFlow [2], Torch [5] and MxNet [3]. AutoVM analyses the computation graph, identifies the data reuse patterns, and identifies the places in the computation graph to insert the offload and prefetch commands. Once AutoVM inserts those commands at appropriate locations in the computation graph, tensor offloads and prefetches are carried out automatically as the computation graph executes. We have also designed an interface that allows machine learning engineers to enable AutoVM with any existing machine learning application by changing only one line of code.

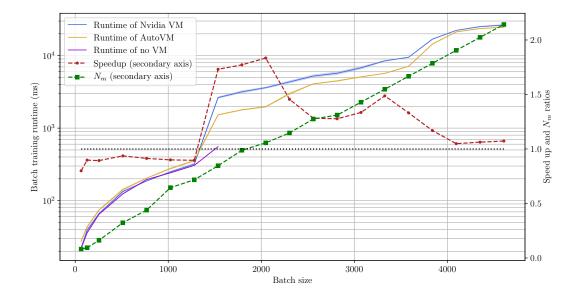

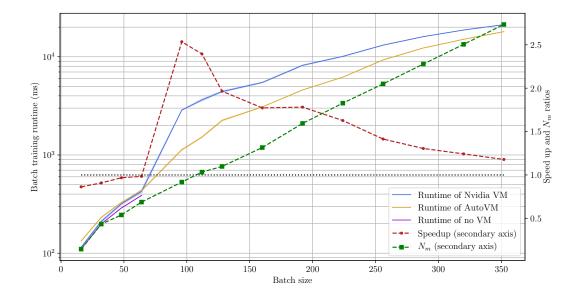

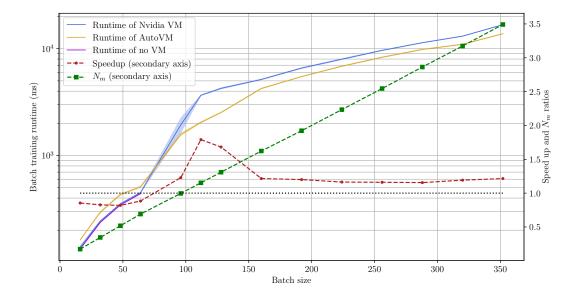

We have integrated AutoVM into TensorFlow to verify its effectiveness in a fully-functional machine learning framework. Our experiments show that our method can achieve a speedup of up to  $2.7 \times$  in VGG-19 training, over Nvidia's default GPU memory management policy.

<sup>&</sup>lt;sup>1</sup>Training is the iterative process where the neural network 'learns'. In each iteration, a batch of images is processed. Successful training requires moderate batch sizes — typically 32 or higher — to be used.

#### 1.1 Motivating example

CNNs have been widely adopted in applications that perform image analysis. A CNN image classifier takes images as input and outputs categorical data that correspond to the classes of subjects present in the input images, for example, "dog", "cat", or "aeroplane". A typical CNN consists of a series of different layers. A layer l takes in the input image  $\mathbf{x}^{(l)}$ , processes it using its set of weights,  $\mathbf{w}^{(l)}$ , and outputs the resulting image<sup>2</sup>  $\mathbf{y}^{(l)}$ . The output is passed on as input to the next layer l+1 as  $\mathbf{x}^{(l+1)}$ . The image-like output from the last convolution layer is flattened to a vector and is then weighted in a fashion similar to the weighted average, to produce the final categorical output. The process in which input travels from the first layer to the last is called inference.

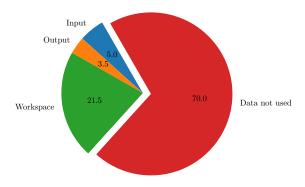

Before a network can be used for inference, however, it has to be trained. During training, a loss function compares the network output with known correct values to measure the network's performance and produces a loss value. All layers' weights are then updated to minimize the loss value and in turn improve the network's performance. The update process of each layer's weights may require the layer's inference output, so layer l's inference output is kept in memory until layer l's weights are updated in training. These previously generated outputs typically occupy a significant amount of memory. For example, in VGG-216 [19], these outputs from a 32-image batch consume around 30GB of memory, constitute over 85% of the total memory usage. Furthermore, training is processed in the opposite order of inference, where the first layers processed in inference are visited the last in training. As such, the time gap between the processing of a layer's inference and training could be significant (hundreds to thousands of milliseconds). Consequently, a substantial amount of data are kept in global memory for an extended amount of time, despite not being actively used.

While the default virtual memory management policy available on modern GPUs can handle workloads that use more memory than what is physically available. The fact that the virtual memory system lacks the domain knowledge of the workloads often encompasses poor memory management decisions. For example, when convolution layer l's output  $\mathbf{y}^{(l)}$  is no longer needed in inference, it can be paged out immediately to free up global memory. However, the fact that Least-Recently-Used (LRU) is the default eviction policy means that even if  $\mathbf{y}^{(l)}$  is the optimal page out candidate,  $\mathbf{y}^{(l)}$  would not be selected for page out as it was recently referenced.

<sup>&</sup>lt;sup>2</sup>Image-like data to be precise. The result, like images, has three channels, but the dimensionality of the third channel might not be three.

<sup>&</sup>lt;sup>3</sup>Although  $\mathbf{y}^{(l)}$  and  $\mathbf{x}^{(l+1)}$  refer to the same piece of data, it is referred to as layer l's output  $\mathbf{y}^{(l)}$  below.

Instead, we propose AutoVM, which smartly chooses data to page out and when. This frees up physical global memory for data that is not being actively accessed. Paged out data are later prefetched into global memory before being referenced in training. Integrated into TensorFlow, our method automates the entire process of data selection for paging so that virtual memory is used more efficiently.

#### 1.2 Contributions

This dissertation makes the following contributions:

- We reverse engineer Nvidia's GPU virtual memory system to reveal some of its performance characteristics,

- We design an active GPU virtual memory management policy AutoVM, to accelerate CNN

training on memory-limited GPUs, by analyzing the computation graphs of CNNs and scheduling

tensor transfers and

- 3. We integrate AutoVM in TensorFlow, a widely used, industrial standard framework, and verified AutoVM is able to deliver non-trivial performance improvement comparing to using Nvidia's default memory management policy.

#### 1.3 Outline of the Dissertation

The remainder of this dissertation is structured as follows. Chapter 2 provides necessary background material on GPUs, neural networks, and TensorFlow so that the remainder of the dissertation can be understood. Chapter 3 describes the design of AutoVM. Chapter 4 presents the results of experiments for the purpose of understanding how Nvidia's managed memory subsystem behaves in practice. This was necessary because Nvidia does not provide any documentation or other information that provides insight of this. The results of these experiments influenced our design and implementation of AutoVM. Chapter 5 presents the implementation of AutoVM. Chapter 6 presents the results of our experiments to evaluate AutoVM. The experiments show AutoVM is able to speed up VGG-19 training by 150.3%, compared to using default Nvidia virtual memory subsystem. We close with concluding remarks and possible future work in Chapter 8.

## Chapter 2

## Background

In this chapter, we present background information on GPUs, deep neural networks (DNNs) and TensorFlow so that the reader can better understand the remainder of this dissertation.

#### 2.1 GPUs

GPUs are highly parallel co-processors, specialized and optimized for graphical processing workloads that involve an extensive amount of parallelizable and in-expensive operations. GPUs have thousands of independent but simple processing cores to process such workloads efficiently.

GPU cores are simpler than CPU cores in that they lack several architectural features that contribute to the performance of CPU cores, such as large, per core caches, branch predictors and complex instruction pipelines. Although a GPU core is weaker than a CPU core, a GPU can support a number of cores that far exceeds the number that CPUs can support. As a result, although per-core performance is lower, parallelizable programs can be executed much faster on a GPU if the program can exploit the many cores available. As co-processors, GPUs have their memory hierarchies separate from the memory hierarchy of the CPU.

GPUs are controlled by programs running on the CPU while having a distinct programming model. Nvidia GPUs use a programming model called CUDA (Compute Unified Device Architecture), which extends the C/C++ programming language to enable general-purpose GPU programming in a familiar CHAPTER 2. BACKGROUND

environment.<sup>1</sup> However, despite CUDA being an extension of C/C++, writing high performance GPU programs is not trivial.

In contrast to CPU architectures that tend to be backwards compatible, GPU architectures can vary quite a bit across generations, and each generation is identified by its *compute capability*, a number. Hence code optimized for one generation is usually not portable to a different generation. For example, devices with compute capability 6.0 and higher have virtual memory support built-in, while those under 6.0 do not. In this discussion we assume capability 7.5 of the *Turing* architecture [15], if not specified otherwise.

The remainder of this section will outline the details of

- GPU hardware architecture,

- software programming model,

- GPU memory hierarchy, and

- libraries for accelerated computing

The main take away is that GPUs are not trivial to program if performance is the key objective. And it is unreasonable to expect those working on machine learning applications to optimize GPU programs for performance, given the complexities of GPUs. Hence, those in the machine learning community rely on libraries that hide the intricacies of GPUs from the machine learning application developers. For the same reason, our objective in this work is to hide the complexities of memory management from the application developers in a software layer that is mostly transparent to developers.

$<sup>^{1}</sup>$ Our description here is limited to Nvidia GPUs, on which this dissertation is based.

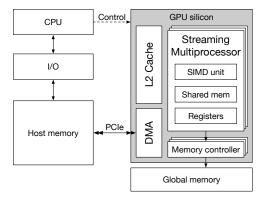

Figure 2.1: High-level GPU architecture.

#### 2.1.1 Hardware architecture

The general architecture of a GPU is shown in Figure 2.1. CPU and GPU have separate off-chip DRAM referred to as *host* memory and *global* memory,<sup>2</sup> respectively. GPU also contains a shared L2 cache accessible to all processing cores. The host and the device are connected via an interconnect such as PCI-Express or NVLink, over which GPUs' DMA (direct memory access) engines transfer data between host memory and global memory. Higher-end GPUs are equipped with two DMAs to support simultaneous bi-directional transfers.

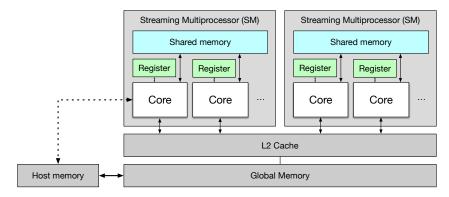

GPU cores are organized into multiple streaming multiprocessors (SMs), each containing tens to hundreds of cores. Each SM also contains a SM-local register file and a small amount of shared memory that is accessible only to the cores within the SM. Figure 2.2 depicts the schematics of Nvidia's TU102 GPU from the Turing family.<sup>3</sup>

#### 2.1.1.1 Streaming multiprocessor

As shown in Figure 2.3, a Turing SM divides the following resources into four partitions:

- 64 CUDA cores, each with one int32 unit and one float32 unit.

- 4 groups of special function units (SFUs) that handle specific maths functions,

- a 64K 32-bit register file,

- a 96KB combined shared memory/L1 cache,

- 4 instructions schedulers.

<sup>&</sup>lt;sup>2</sup>This GPUs' on-board memory is also referred to as the device memory. We will use the term global memory in this dissertation.

<sup>&</sup>lt;sup>3</sup>Turing is the newest GPU architecture, as of Aug 2019.

Figure 2.2: Schematics of the TU102 GPU. All SMs share the L2 cache located in the center. Green blocks portray SIMD cores within SMs.

Figure 2.3: Structure of the Turing streaming multiprocessor.

These resources are local to an SM, and are not shared with other SMs in the GPU. Each SM also has one RT core that is used for ray tracing, but this is irrelevant to this project.

Figure 2.4: CUDA memory hierarchy.

#### 2.1.1.2 Memory hierarchy

Data accessed by GPU cores can reside in a number of different types of memory. Table 2.1 summarizes the performance characteristics of the memories available on Nvidia Turing GPUs.

Local variables are typically stored in registers that offer very fast access. GPUs have many more registers than CPUs. Nevertheless, when a thread uses too many local variables, the register contents get spilled over into L1 and L2 caches and ultimately, global memory.

Each SM also has a fast (around 19 cycles) local scratch pad memory called *shared memory*. The key challenge with this type of memory is that it is relatively small (at most 96KB per SM) and is entirely managed by the programmer. Programmers have to decide which data resides there and when, and explicitly copy data into and out of shared memory.

Otherwise, all data reside in global memory, which can vary in size; for instance our GPU has 11GB of global memory while the highest-end GPU has 48GB.<sup>4</sup> Access to global memory is significantly slower than that of shared memory: an access to global memory typically takes over 250 cycles to complete.

GPU hardware uses three approaches to mitigate global memory access latencies. First, 32 words can be accessed in parallel from 32 adjacent cores, if the 32 words fall onto an aligned, continuous region. Such an access pattern is referred to as *coalesced access*. It is thus beneficial for the programmer to structure a program's data so that accesses to the data occurs in a coalesced fashion. Otherwise, access latencies can be significantly larger — in the worst case, accesses latencies to randomly located data will be 32 times higher than coalesced accesses.

<sup>&</sup>lt;sup>4</sup>Quadro RTX6000 is the highest-end GPU listed for sale, as of the writing.

|               |                      | Perform                 | ance             |

|---------------|----------------------|-------------------------|------------------|

|               | Size                 | Access latency (cycles) | Bandwidth (GB/s) |

| L1 cache      | 64 KB (per SM)       | 32                      | 177              |

| L2 cache      | $4~\mathrm{MB}$      | 200                     | 2,155            |

| Shared memory | 32 or 64 KB (per SM) | 19                      | 13,800           |

| global memory | 11 GB                | 300                     | 616              |

Table 2.1: Access latency and bandwidth of memories available on Nvidia Turing GPUs.

Secondly, GPUs can perform context switches very quickly — i.e., typically in one cycle. As such, if a thread issues a read to global memory, a context switch occurs immediately to allow another thread to run while the first accesses global memory. This implies that the programmer will need to structure their code to use many more threads as there are cores to ensure there always are ready thread blocks to schedule.

Finally, a GPU has multiple caches for faster accesses: L1 caches, (96 KB per SM) are owned privately by each SM; a single L2 cache (4 MB), with access latency around 200 cycles, is shared between all SMs onboard.<sup>5</sup> The caches are managed by the hardware transparent to the applications. However, it should be pointed out that L1 caches are typically disabled for program data on modern GPUs.<sup>6</sup>

#### 2.1.1.3 Hardware thread execution

GPU programs are expected to be structured to execute with many thousands of threads. Once a thread starts executing on an SM, it will remain on that SM for the duration of its life cycle; i.e., it will never be migrated onto a different SM.

The hardware executes groups of 32 threads in lock step on adjacent GPU cores. That is, threads [n mod 32] to [(n+31) mod 32] execute the same set of instructions at the same time in SIMD (single instruction multiple data) fashion. Such a group of 32 threads is called a warp. A warp is the basic unit of scheduling and context switching. This makes the hardware more efficient because it allows 32 cores to share a single instruction stream.

Different threads in a warp may take different branches, and if they do, it is called *thread divergence*. Thread divergence causes execution to be slower because all threads in a warp share the same instruction stream. For example, in code executing C = (cond)? A(): B(), when some threads in a warp

<sup>&</sup>lt;sup>5</sup>The Quoted amounts are based on Turing architecture GPUs.

<sup>&</sup>lt;sup>6</sup>This is because L1 cache and shared memory are implemented using the same memory device. CUDA applications typically use that entire space for shared memory, thus there is no space to support L1 caching.

execute A, the other threads are blocked and then continue to execute B when A has completed executing.

When B is being executed, the A-executing threads will be blocked.

#### 2.1.2 Programming model

Since GPUs are CPU-controlled co-processors, all general-purpose GPU programs consist of two parts, namely:

- 1. Kernels, which are CPU-invoked GPU functions running in parallel by multiple GPU threads,

- 2. CPU code that issues instructions to CUDA drivers to control GPU behaviour, such as kernel launches, memory allocations and deallocations, memory copies, and synchronization.

To illustrate, a program that does matrix multiplication,  $C = A \cdot B$ , involves the following steps, assuming matrices A and B reside in host memory:

- 1. CPU instructs memory be dynamically allocated in global memory;

- 2. CPU initiates the data transfer of A and B from the host memory to global memory;

- 3. CPU launches a matrix multiply kernel on the GPU;

- 4. GPU executes the matrix multiplication kernel using its thousands of cores;

- 5. CPU initiates the transfer of result C to the host memory and the deallocation of the memory buffer in global memory.

In the example above, only step 4 executes on the GPU. However, if step 4 takes a significant proportion of run time and the GPU executes matrix multiply much faster than the CPU, offloading the matrix multiply onto the GPU can boost performance considerably.

In the next sub-sections, we describe kernel launch, thread hierarchy, scheduling, and streaming.

#### 2.1.2.1 Kernel launches

Launching a GPU kernel takes the form of an ordinary function call with additional *launch parameters*. Unlike a regular function invocation, CUDA kernel launches always return void, and always return immediately. That is, kernels execute asynchronously in parallel to subsequent CPU program execution. The extra launch parameters specify how the launching kernel should be executed. The two required parameters describe how many threads the kernel should execute with as well as how they are organized, something referred to as the *thread hierarchy*.

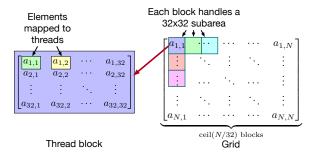

Figure 2.5: Thread hierarchy mapped to a matrix addition problem.

#### 2.1.2.2 Thread hierarchy

Threads must be logically arranged in 1D, 2D or 3D *blocks* by the programmer. The Nvidia architectures released so far limit the maximum number of threads in one block to 1,024.

Blocks are logically organized into 1D, 2D or 3D grids. The limit on the number of blocks in a gird is quite high to support mapping large problems.<sup>7</sup> Threads can locate their location within the blocks and grids by using index values provided by the CUDA runtime. When a kernel is launched, each thread executes the same kernel and can determine what data to process based on its position within the thread hierarchy. Figure 2.5 depicts a possible thread hierarchy for matrix addition: every thread is assigned to calculate one element  $A_{i,j} = B_{i,j} + C_{i,j}$  in the resulting matrix. Since up to 1,024 threads can be in one block, the programmer could appoint each block to process a 32 × 32 sub-matrix of A. As such, one  $N \times N$  matrix is processed with  $N^2$  threads, arranged in a  $(\lceil N/32 \rceil, \lceil N/32 \rceil)$  grid of blocks.

#### 2.1.2.3 Scheduling on GPUs

Each block is dispatched to a streaming multiprocessor that has sufficient resources available to execute the block. Once a block is dispatched to a SM, it remains on that SM until it finishes. Blocks will be queued when no SM has sufficient resources to support the execution. At every issue cycle, warp schedulers in an SM select warps for execution, whose resource or data dependencies are satisfied.

#### 2.1.2.4 Stream interface

Abstractly, streams are GPU task queues on which CPU-submitted CUDA tasks are queued. A CUDA program can allocate multiple streams and queue tasks onto different streams.<sup>8</sup> But the program does not have direct control over whether tasks are executed concurrently or not. Launching

$<sup>^72^{32} - 1</sup>$  blocks in the x-dimension and 65,536 blocks in the y and z dimensions.

$<sup>^8\</sup>mathrm{The}$  default stream is used, if no target stream is specified when making CUDA calls.

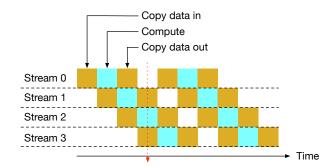

Figure 2.6: Illustration of pipelining using four streams.

tasks onto different streams is a necessary but not sufficient condition for the tasks to be executed in parallel on GPU.

Streams are mainly used to implement piplining to achieve parallel data transfer and computation. Figure 2.6 depicts a pipeline using streams: yellow blocks represent memory copies while cyan ones represent computations. Each stream repeatedly copies data in from the CPU, does the computation, and copies the data out. The memory copies and computation tasks are scheduled in a fashion so that DMA engines and processing cores are kept busy at all times. For instance at the beginning, after stream 0 copies its data to global memory and starts its computation, stream 1 starts using the DMA engine for copying its data (shown as the first yellow block on the second row). Ideally, after stream 1 has finished copying, the computation of stream 0 also finishes, so that stream 1 can start its calculation. This process is repeated such that the compute cores are continually running at full speed as if no memory transfers have taken place.

#### 2.1.3 Memory management

Prior to CUDA 6.0, hosts and devices could only access data that are stored in their respective memory devices. For example, SMs could only access data stored in global memory but not in host memory. CUDA 6.0 introduced unified memory<sup>9</sup> that relaxed this limitation and allowed data to be accessible from any processor in the system, regardless of the data's storage location. However, if the data is not in the memory of the accessing processor, it is transferred to the memory of the accessing processor. For instance, if a GPU program accesses a piece of memory that resides in host memory, but not in global memory, CUDA runtime will copy the data to global memory via the interconnect.

Newer GPUs starting from compute capability 6.0, with CUDA 8.0, are equipped with full virtual memory support, with something Nvidia calls "managed memory.<sup>10</sup>" Nvidia also allows users to guide the virtual memory system to achieve more efficient memory management. This section provides background on GPU virtual memory system. Details on the older GPUs that do not support virtual memory are omitted from the discussion as they are not the primary concern of this work.

#### 2.1.3.1Virtual memory support

GPUs with compute capability 6.0 and higher, have full paging capability and support 49-bit virtual address translation. Memory pages<sup>11</sup> can physically reside any host memory or global memory and be migrated to any device (CPU or GPU) upon request. For example, SMs on a GPU can access data stored in host memory through demand paging. Like CPU virtual memory, CUDA applications can access a memory space that is much larger than what is physically available on the GPU, something often referred to as memory over-subscription. In addition to the default memory management policy, users can use advise and explicit prefetching to guide the runtime to manage GPU virtual memory better.

#### 2.1.3.2User control of virtual memory

As with CPU virtual memory, the keys to good memory performance include preventing page faults and keeping data local to the accessing processor. The default memory management policy often makes suboptimal paging decisions because it has no understanding of the running workload and relies only on

<sup>&</sup>lt;sup>9</sup>CUDA version refers to the runtime version. Unified memory is enabled by the CUDA runtime as a software functionality that does not require extra hardware support.

<sup>&</sup>lt;sup>10</sup>Unlike the unified memory, managed memory support requires extra hardware, represented by the newer compute capability.

11 The page size is variable and cannot be set by users.

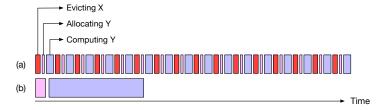

Figure 2.7: Example of computing with and without explicit memory control. (a) shows the case where X is not explicitly offloaded and no free physical page is available to accommodate the newly produced data. To allocate a physical page for Y, a page of X needs to be evicted from physical global memory. The corresponding computation cannot start until X's page is evicted and Y's page allocated. This process is repeated for every page of Y. While in case (b), if X is explicitly transferred out, then the required physical pages of Y can be allocated quickly and Y's computation can proceed non-stop. As a result, the time taken in case (b) is much shorter than (a).

a general heuristic. Nvidia provides two runtime library functions, that allow the program to guide the default memory management policy: cudaMemAdvise() and cudaMemPrefetchAsync().<sup>12</sup>

- cudaMemAdvise() is used to provide a hint to the virtual memory system, how and from where target data will be accessed.

- cudaMemPrefetchAsync() prefetches data to one of the memories (host memory or global memory) by initiating an asynchronous data migration. Prefetching can be used to improve data locality and avoid page faults. Data transfers are asynchronous: memory transfers execute in parallel with computations to hide the transfer latencies. In practice, this runtime library function call can be either used to evict data from global memory or prefetch to global memory.

#### 2.1.3.3 Benefits of user control

It is beneficial to manually control memory when the CUDA application uses more virtual memory than the physical global memory. For example consider the scenario in Figure 2.7: suppose data X was just produced in global memory, and will not be reused in the near future. Meanwhile, a computation kernel is producing data Y, but there is not enough memory to store both X and Y physically in global memory.

1. If X had been previously migrated out from global memory to host memory, the physical pages storing X in global memory can be freed to make space to store Y's pages physically in global memory allowing the computations to proceed at full speed. This scenario is shown in row (b) of Figure 2.7.

<sup>&</sup>lt;sup>12</sup>Suboptimal invocations of advise and prefetch may negatively affect performance.

- 2. Otherwise, physical pages have to be evicted to host memory, (red-coloured blocks show the time used for evicting pages) to make space for the newly generated data, a page at a time. In particular, the GPU is performing the following steps repeatedly for every page of Y when first accessed:

- a page fault occurs since it does not in global memory,

- a victim page for eviction to host memory, needs to be selected because no free physical page is available,

- the data stored in that page is transferred to host memory,

- $\bullet$  the evicted physical page is deallocated, and allocated a page for Y, and

- the computation continues.

Every step blocks the next; as a result, the performance is considerably worse compared to the first case where no eviction is needed during the production of Y.

Although X would be the best candidate for eviction since it will not be accessed in the near future, it is unlikely to be selected for eviction by the default memory management policy, as it was recently referenced. Hence, manually controlling memory by issuing an eviction request for X will benefit performance when the global memory is over-subscribed.

#### 2.1.4 GPU performance issues

GPUs are not trivial to program if good performance is the objective, because of the complex architectures of GPUs. In particular, some of the following issues need to be taken into account:

- Coalesced memory access Global memory accesses need to be coalesced to attain high memory throughput. That is, threads in a warp need to access memory addresses that fall into aligned and continuous 32, 64 or 128 bytes regions.

- Thread divergence Although the thread execution model allows the threads in a warp to take different branches, divergent threads can negatively impact performance by up to a factor of 2.

- **Shared memory** Programs often use shared memory as scratch pads, and the shared memory is managed by the programmer. The shared memory needs to be used wisely as it is limited in size. Furthermore, access latencies of shared memory will be suboptimal if threads in one warp access different addresses within the same shared memory bank. Such behaviour is called shared memory bank conflict and should be avoided.

- Occupancy Occupancy measures the level of resource usage in SMs. As explained in §2.1.1.2, global memory access latencies of a warp can be hidden by executing other warps' computations. It is

thus often beneficial to use many threads so that when some access memory, there are other threads to schedule to hide global memory access latency. However, the more resource (registers or shared memory) a thread uses, the fewer threads can reside in a SM. This means the programmer has to be using the resources wisely so that there are enough threads in a SM to hide global memory access latencies.

17

The bottom line: a systematic understanding of the underlying GPU architecture is crucial for writing high-performance GPU programs. As a result, libraries that hide the system's intricacies are typically preferred. Machine learning engineers are typically not system experts, and hence they cannot be expected to write well-performing CUDA applications. As such, they rely on libraries that were written by system experts.

#### 2.1.5 Accelerated libraries

Nvidia has released accelerated libraries that contain highly optimized functions useful in a variety of domains including signal processing, scientific computing and deep learning. These library functions do not require the machine learning engineers to launch CUDA kernels (that requires the additional launch parameters) but instead offer wrapper functions that invoke appropriate kernels. In fact, every library function is backed by multiple implementations that are optimized for specific configurations and the appropriate implementation is invoked. For example, the function for matrix multiplication has multiple implementations, optimized for different matrix shape configurations. On invocation, the library runtime applies heuristics to determine the implementation that best suit the matrix shape configuration.

### 2.2 Deep neural network

Neural networks, inspired by brain neurology, are a subset of machine learning algorithms that can "learn" from examples and perform specific tasks on new data. For example, a classifier can learn to categorize architectural styles of houses by analyzing example images that have been manually labelled; e.g., *Russian*, *gothic* or *baroque*. The classifier learns the traits specific to each of the architectural styles without requiring any prior knowledge of architecture or manual instructions.

Neural networks are built by arranging *layers* in specific orders. A "layer" is an abstraction of a math operation that transforms its input in a specific way. Each layer uses  $weights^{13}$  to affect the

<sup>&</sup>lt;sup>13</sup>A few types of layer do not use weights.

| Symbol          | Usage                      | Symbol         | Usage                                      |

|-----------------|----------------------------|----------------|--------------------------------------------|

| $\overline{x}$  | Input                      | k              | Current output channel                     |

| $\overline{y}$  | Output                     | K              | Total output channels                      |

| $\overline{w}$  | Weight                     | p              | Current output height position             |

| d or $\partial$ | Derivative/Gradient        | q              | Current output width position              |

| $f^{(l)}$       | Layer $l$ 's math function | $\mathcal{L}$  | Loss function                              |

| $\alpha$        | Learning rate              | $\overline{x}$ | Gradient $\partial \mathcal{L}/\partial x$ |

| $\overline{N}$  | Batch size                 | i, j           | Indices                                    |

| $\overline{H}$  | Input image height         | l              | Layer number                               |

| $\overline{W}$  | Input image width          | Θ              | Set of all trainable weights               |

| C               | Total input channels       | Bold type      | N-dimensional array (or tensor)            |

Table 2.2: Mathematical symbols used in the dissertation.

transformation. Inputs and outputs of neural networks are also task-specific. For example, an image classifier takes in images and outputs the classes of objects in the images that were input. Specifically, the house style classifier outputs (for each image input) a 3-element vector, with each element equal to the predicted probability that the input image contains Russian, gothic or baroque architecture.

A neural network has to be trained before it can be used for *inference*. Inference is the process where inputs propagate through the layers to produce the network output. *Training* refers to the process in which the network corrects its weights by taking into account mistakes it has made during the previous inferences.

Deep neural networks (DNNs) refer to neural networks that have many layers. Our work focuses on convolutional neural networks (CNNs), a subset of DNNs, that have been widely applied in analyses of visual imagery.

In this section, we describe the mechanics and workload of CNNs. Specifically, the following subsections provide details on

- types of layers used in CNN and their performance characteristics,

- the inference and training process, and

- data flow in CNN training.

Table 2.2 summarizes the symbols used in our formulas<sup>14</sup> in the text that follows.

<sup>&</sup>lt;sup>14</sup>In the dissertation, bias terms are often omitted for simplicity, we assume that the data and weight tensors are augmented to include the effect of bias terms.

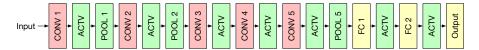

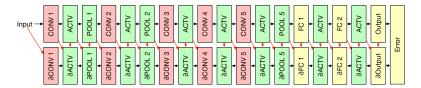

Figure 2.8: Layer structure of AlexNet. The colours in the figure represent the estimated run times of layers: red:long, yellow:medium, green:short.

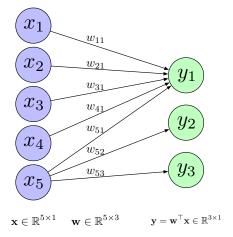

Figure 2.9: Illustration of a linear layer that takes five input and outputs three weighted results.

#### 2.2.1 Layers in neural networks

A layer abstracts a mathematical operation performed on its inputs; its output is passed to subsequent layers as inputs, for further processing. Figure 2.8 depicts a typical CNN with four types of layers that are used in CNNs. The following subsections describes these layer types, as well as their performance characteristics.

#### 2.2.1.1 Fully connected layers

A fully connected (FC), or linear layer, takes an input and applies a weight function to produce an output. Figure 2.9 illustrates a fully connected layer that takes five inputs and produces three outputs (some edges are omitted for cleanliness). In the example, the layer's input is a  $5 \times 1$  vector  $[x_1, \ldots, x_5]^{\top}$ , which is weighted by a  $5 \times 3$  weight matrix (  $\vdots$  ), and the output is a  $3 \times 1$  vector  $[y_1, y_2, y_3]^{\top}$ . Generally, a fully connected layer that takes in a n-element vector and outputs a m-element vector  $\mathbf{y}$ , uses a  $m \times n$  weight matrix  $\mathbf{w}$ . The math operation, written in its matrix form, is

$$\mathbf{y} = \mathbf{w}^\top \cdot \mathbf{x}$$

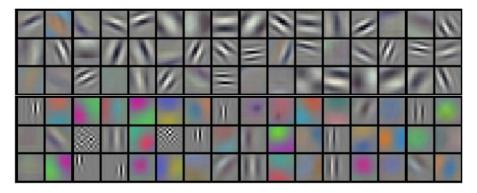

Figure 2.10: Example filters learned by the first convolution layer in Alexnet [13]. Each of the 96 filters is sized  $11 \times 11 \times 3$ . Note that some filters focus on discovering lines and some extract shape and colour information.

In practice, multiple inputs are stacked together to form a matrix, hence, the computation of a fully connected layer is a matrix multiplication, an operation that can be parallelized in a straight forward way. Matrix multiplication has a time complexity of  $O(n^3)$ .

#### 2.2.1.2 Convolution layer

Convolution layers are used to extract local features, like lines in a particular direction or a blotch of some colour, by convolving the input with its weights (also called filters). Input images to a convolution layer are typically represented by three-dimensional arrays, where the first two dimensions are the width and height, and the third dimension if often referred to as *channel*. Colour images typically contain three channels, namely red, green and blue. The value at any given point (p,q) of channel k, in the convolution result, is defined as

$$y_{p,q,k} = \sum_{c=1}^{C} \sum_{s=-a}^{a} \sum_{t=-b}^{b} \mathbf{w}_{s,t,k} \cdot x_{p-s,q-t,c}$$

where x is the image input,  $\mathbf{w}$  is the 3D filter that is spatially sized as  $2a \times 2b \times K$ , and y is the convolution result, also called the *feature map*. The parameter c in the formula refers to *channel* in the input image.

The workload of a convolution computation is demanding on both compute and memory resources. Many parallel algorithms, including implicit GEMM, Winograd method [24] and FFT, have been developed to accelerate convolution computations. Implicit GEMM, for example, reorders the image inputs and filters in a way such that the convolution can be computed with matrix multiplications. Some parallel algorithms, like FFT, have large memory requirements that can be in the gigabyte range. Convolution

Figure 2.11: Feature maps produced by later convolution layers. Yosinski et al. [26].

results (i.e., feature maps) can also consume a significant amount of memory. For example, in network VGG-16 [19], the size of all feature maps generated from one  $224 \times 224 \times 3$  image is around 100MB, while all weights in the network consume only about 50MB. It is for this reason we target feature maps when optimizing the memory management.

#### 2.2.1.3 Activation layer

Activation layers apply a non-linear transformation to their inputs without using weights. Non-linear activation is crucial to CNNs, as according to universal approximation theorem [8], non-linear neural networks can approximate any function. Without activation, neural networks can only represent linear systems. Activation is applied to every element in the input, that is

$$\mathbf{y} = \sigma(\mathbf{x})$$

where  $\mathbf{x}$  is the input,  $\sigma(\cdot)$  is an element-wise non-linear function and  $\mathbf{y}$  is the output. In many CNNs,  $\text{ReLU}(x) = \max(0, x)$  is used as the activation function because both the function and the function gradient are relatively inexpensive to compute compared to other activation functions like  $\text{tanh}(\cdot)$ .

The computation of ReLU activation is trivial and embarrassingly parallelizable. Furthermore, since the output shape is the same as that of the input, activation can be implemented as an in-place operation to save space.

#### 2.2.1.4 Pooling layer

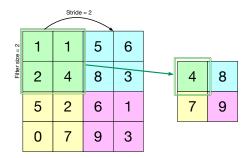

Pooling is used to progressively reduce the size of the feature maps generated by convolution, and in turn reduces the number of weights needed in the network. The most commonly used configuration is max pooling with a filter size of  $2 \times 2$  and a stride of 2. This means that the input is partitioned into  $2 \times 2$  sub-matrices, and for every sub-matrix, only the largest element is kept. As illustrated in Figure 2.12,

Figure 2.12: Illustration of pooling with filter size 2 and stride 2.

pooling under this configuration effectively removes 75% of the input data. The computation required for pooling is trivial and easily parallelizable.

#### 2.2.1.5 CNN structure

Convolutional neural networks contain chains of layers arranged in specific sequences. For example, AlexNet [13] chains five instances of convolutional segments with three fully connected layers, as illustrated in Figure 2.8 (on page 19). A network, in which layer l's output is only taken as input by layer l + 1, is called a *linear network*. In non-linear networks, however, layer l's output is used by multiple other layers. Our work focuses on linear CNNs.

#### 2.2.2 Inference and Training

Neural networks have to be trained before they can be used for inference. Below we describe how both inference and training work.

#### **2.2.2.1** Inference

Inference, also known as *forward propagation*, refers to the process of propagating the network input through the layers. The input is transformed by each layer from the first to the last, where the inference output is produced. The inference process can be abstracted as compounding the layers' corresponding mathematical functions:

inference result =

$$\mathcal{F}$$

(input,  $\mathbf{\Theta}$ ) =  $f^{(l)} \circ f^{(l-1)} \circ \cdots \circ f^{(2)} \circ f^{(1)}$  (input,  $\mathbf{\Theta}$ )

where  $f^{(l)}$  represents the math function of layer l, and  $\Theta$  is the set of all trainable weights,  $\Theta = \{\mathbf{w}^{(i)} | \forall i = 1 \dots l\}.$

#### 2.2.2.2 Training

Training calibrates the network weights using the inference result. During training, labelled data is fed into the network for inference. The inference result is then compared against the known correct values by a loss function  $\mathcal{L}$ , which outputs a numerical loss value that measures "how accurate" the inference results are. For example, if the house style classifier correctly identified the style, then the loss will be small; whereas if it categorized Russian design to be baroque, the loss would be larger to reflect the error.

$$\begin{aligned} & loss = \mathcal{L}(inference \ result, data \ labels) \\ & = \mathcal{L}\left[\mathcal{F}\left(input, \boldsymbol{\Theta}\right), data \ labels\right] \end{aligned}$$

The training objective is to minimize the loss of a neural network by appropriately adjusting the network weights. Ideally, the trained weight is the one, among all possible weights, that leads to the least loss value:

$$\Theta_{opt} = \underset{\Theta \in \mathbb{R}}{\operatorname{argmin}} \ \mathcal{L}\left[\mathcal{F}\left(\operatorname{input},\Theta\right), \operatorname{data\ labels}\right]$$

Thus, loss functions quantify the network accuracy and turn training into a numerical optimization process.

#### 2.2.3 Gradient descent

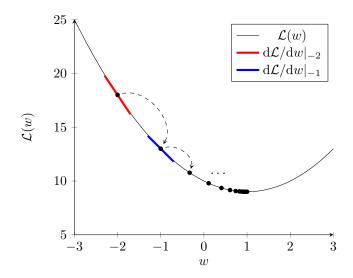

Although it is unclear whether a neural network's loss function is convex; convex optimization techniques have been successfully applied to minimize the loss. Gradient descent is an optimizing technique for finding minima in convex problems and is widely used in neural network training.

The algorithm employs the fact that the global minima of a convex function can be approached iteratively by moving along the function's curve, in the negative direction of its gradient. The gradient of a function at a point indicates the direction of the fastest descent along the function at that point.

Consider the quadratic function  $\mathcal{L}(w)$  depicted in Figure 2.13, and assume weight w is initially set to -2. Intuitively, w's value needs to be increased to reach  $\mathcal{L}$ 's minima. The gradient of  $\mathcal{L}$ , at -2 is -6, denoted by the slope of the thick red line. The value of w should be increased to be closer to  $\mathcal{L}$ 's minima. A common approach is to adjust the value of w by  $\mathcal{L}$ 's gradient scaled with  $-\alpha$ . If  $\alpha = 1/6$ ,

Figure 2.13: Applying gradient descent to a quadratic function (convex). The amount moved is  $\alpha \cdot dL/dw$ .

then the value of w is increased by 1 to -1 in the first iteration. The process is then repeated until the  $\mathcal{L}(w)$  converges to its minima, as depicted by the black dots.<sup>15</sup>

The update in every iteration, written formally, is:

$$w_{new} \leftarrow w_{old} - \alpha \cdot \frac{\mathrm{d}\mathcal{L}}{\mathrm{d}w}\Big|_{w_{old}}$$

(2.1)

where  $\alpha$  is called the *learning rate*, a *hyper-parameter* that is manually set before training and will not be tuned by the gradient descent process. Finding optimal  $\alpha$ 's remains as an active research topic [28] [27]. Some optimization technique, like ADAM [12] that extends gradient descent, adjusts the learning rate during the iterative descent process.

Equation (2.1) adjusts only one weight. In practice, weights have more elements and every element is updated based on the partial derivative of the loss function with regard to itself:

$$w_i \leftarrow w_i - \alpha \cdot \frac{\partial \mathcal{L}}{\partial w_i}, \ \forall w_i \in \mathbf{\Theta}$$

(2.2)

<sup>&</sup>lt;sup>15</sup>In practice, the training process is stopped when the loss converges to a small value.

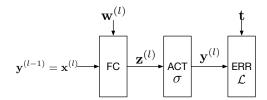

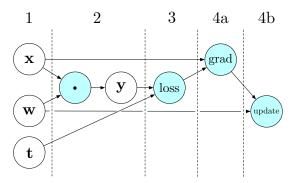

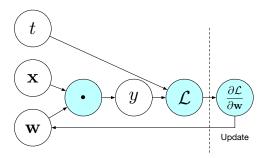

Figure 2.14: Example dataflow of the last two layers of a CNN: a fully connected and an activation layer.  $\mathbf{z}^{(l)} = (\mathbf{x}^{(l)})^{\top} \cdot \mathbf{w}^{(l)}, \mathbf{y}^{(l)} = \sigma(\mathbf{z}^{(l)})$ .  $\mathcal{L}$  represents the loss function that measures the activation result  $\mathbf{y}^{(l)}$  against known data label  $\mathbf{t}$ .

#### 2.2.3.1 Gradient calculation

Training adjusts all the weights in the network to minimize the loss, improving inference performance. As mentioned in §2.2.2.1, inference can be abstracted as compounding layers' corresponding math functions, allowing us to apply the chain rule to find the gradient of each weight element.<sup>16</sup>

The rules for gradient calculation is illustrated using a simple example below; we will also generalize the rules in the next subsection. Figure 2.14 (on page 25) shows the last two layers of a CNN, consisting of a fully connected layer and an activation layer. The fully connected layer takes in  $\mathbf{x}^{(l)}$ , and outputs  $\mathbf{z}^{(l)} = \mathbf{w}^{(l)}\mathbf{x}^{(l)}$ . The activation layer then applies the non-linear function  $\sigma$  to its input,  $\mathbf{z}^{(l)}$ ; its output  $\mathbf{y}^{(l)}$  is then assessed by a square loss function  $\mathcal{L} = \frac{1}{2}\sum_{i=1}^{N}(t_i - y_i)^2$ , a typical error function used in regression tasks.<sup>17</sup>

In the deduction that follows,  $\bar{\mathbf{a}}$  is used to denote the gradient of  $\mathcal{L}$  with regarding to  $\mathbf{a}$ , i.e.,  $\bar{\mathbf{a}} = \{\partial \mathcal{L}/\partial a_i \mid \forall a_i \in \mathbf{a}\}$ .  $\mathbf{t}$  is the vector of known values of data labels.  $\|\mathbf{a}\|_2^2$  denotes the square of  $\mathbf{a}$ 's Euclidean norm,  $\|\mathbf{a}\|_2^2 = \left(\sqrt{\sum_i a_i^2}\right)^2 = \sum_i a_i^2, \forall a_i \in \mathbf{a}$ .

To summarize, the dataflow in Figure 2.14 is:

$$\mathbf{z}^{(l)} = (\mathbf{x}^{(l)})^{\top} \cdot \mathbf{w}^{(l)};$$

$$\mathbf{y}^{(l)} = \sigma(\mathbf{z}^{(l)})$$

$$\mathcal{L} = \frac{1}{2} \sum_{i=1}^{N} (t_i - y_i^{(l)})^2 = \frac{1}{2} \|\mathbf{t} - \mathbf{y}^{(l)}\|_2^2$$

<sup>&</sup>lt;sup>16</sup>Chain rule is used for finding derivatives of compound functions. Specifically,  $\frac{\mathrm{d}}{\mathrm{d}x}f\circ g(x)=\frac{\mathrm{d}f}{\mathrm{d}g}\frac{\mathrm{d}g}{\mathrm{d}x}$ . In multi-variable functions, the chain rule is applied to each constituent function. For example,  $\frac{\mathrm{d}}{\mathrm{d}t}h(f(x),g(x))=\frac{\partial h}{\partial f}\frac{\mathrm{d}f}{\mathrm{d}x}+\frac{\partial h}{\partial g}\frac{\mathrm{d}g}{\mathrm{d}x}$ .

<sup>&</sup>lt;sup>17</sup>The fraction in front cancels out when taking the gradient of the loss function.

The goal of gradient descent is to find the gradient of  $\mathcal{L}$  with regard to weight  $\mathbf{w}^{(l)}$ . Specifically, the chain rule gives us

$$\frac{\partial \mathcal{L}}{\partial \mathbf{w}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{y}^{(l)}} \cdot \frac{\partial \mathbf{y}^{(l)}}{\partial \mathbf{z}^{(l)}} \cdot \frac{\partial \mathbf{z}^{(l)}}{\partial \mathbf{w}^{(l)}}$$

The calculation of weight gradient  $\frac{\partial \mathcal{L}}{\partial \mathbf{w}^{(l)}}$  can be split into the following steps. For better readability, we colour the steps following the derivation steps of,  $\frac{\partial \mathbf{y}^{(l)}}{\partial \mathbf{z}^{(l)}}$ ,  $\frac{\partial \mathbf{z}^{(l)}}{\partial \mathbf{w}^{(l)}}$  and  $\frac{\partial \mathbf{z}^{(l)}}{\partial \mathbf{x}^{(l)}}$ :

$$\overline{\mathbf{y}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{y}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathcal{L}} \cdot \frac{\partial \mathcal{L}}{\partial \mathbf{y}^{(l)}} = \mathbf{1} \cdot \left( \mathbf{y}^{(l)} - \mathbf{t} \right)$$

(2.3)

$$\overline{\mathbf{z}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{z}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{y}^{(l)}} \cdot \frac{\partial \mathbf{y}^{(l)}}{\partial \mathbf{z}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{y}^{(l)}} \cdot \frac{\partial \sigma(\mathbf{z}^{(l)})}{\partial \mathbf{z}^{(l)}} = \overline{\mathbf{y}^{(l)}} \cdot \sigma'\left(\mathbf{z}^{(l)}\right)$$

(2.4)

$$\overline{\mathbf{w}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{w}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{z}^{(l)}} \cdot \frac{\partial \mathbf{z}^{(l)}}{\partial \mathbf{w}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{z}^{(l)}} \cdot \frac{\partial \left[ (\mathbf{x}^{(l)})^{\top} \cdot \mathbf{w}^{(l)} \right]}{\partial \mathbf{w}^{(l)}} = \overline{\mathbf{z}^{(l)}} \cdot (\mathbf{x}^{(l)})^{\top}$$

(2.5)

Equation (2.5) shows that computing the weight gradient of layer l requires  $\overline{\mathbf{y}^{(l)}}$  and  $\mathbf{x}^{(l)}$ . Similarly, updating the weight gradient of layer l-1 will demand  $\overline{\mathbf{y}^{(l-1)}}$ , as presented below:

$$\overline{\mathbf{y}^{(l-1)}} = \overline{\mathbf{x}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{z}^{(l)}} = \frac{\partial \mathcal{L}}{\partial \mathbf{z}^{(l)}} \cdot \frac{\partial \mathbf{z}^{(l)}}{\partial \mathbf{x}^{(l)}} = (\mathbf{w}^{(l)})^{\top} \cdot \overline{\mathbf{z}^{(l)}}$$

(2.6)

(2.7)

The resulting gradient  $\overline{\mathbf{x}^{(l)}}$  is often referred to as the *data gradient* or  $d\mathbf{x}$  because it is calculated based on the input data. It is propagated backwards to layer l-1 as  $\overline{\mathbf{y}^{(l-1)}}$  (or  $d\mathbf{y}^{(l-1)}$ ).

In summary Equation (2.3) and Equation (2.5) show that the following operands are required to update the weights of a fully connected layer l:<sup>18</sup>

- $\overline{\mathbf{y}^{(l)}}$ : The gradient of error w.r.t.  $\mathbf{y}^{(l)}$ , or else known as  $d\mathbf{y}$ ,

- $\mathbf{y}^{(l)}$ : Layer l's input during inference

- $\mathbf{w}^{(l)}$ : Layer l's weight

- $\mathbf{x}^{(l)}$ : Layer l's input during inference

$<sup>^{18}</sup>$ Not all types of layers require all the data listed. For example, the gradient calculation of convolutions does not require y.

#### 2.2.3.2 Generalized gradient calculation

In general, if  $x_j$  has contributed to output element  $y_k$  in inference,  $y_k$  will influence the gradient of  $x_j$  during the gradient computation. The gradient of  $\mathcal{L}$  w.r.t.  $x_j$  is the sum of all  $y_k$ s that  $x_j$  has influenced during inference, i.e.,

$$\overline{x_j} = \sum_k \overline{y_k} \cdot \frac{\partial y_k}{\partial x_j}$$

written in vector form,

$$\overline{\mathbf{x}} = \frac{\partial \mathbf{y}}{\partial \mathbf{x}}^{\top} \overline{\mathbf{y}} \tag{2.8}$$

where  $\partial \mathbf{y}/\partial \mathbf{x}$  is often denoted as the *Jacobian matrix* where  $J_{i,j} = \partial y_i/\partial x_j$ . The calculation of multiplying the Jacobian with vector  $\mathbf{dy}$  is often referred to as taking a *Vector-Jacobian product* or VJP.

The two examples below show the gradient computation methods of an activation layer and a fully connected layer.

- In activation layers, where  $x_i$  contributes only to  $y_i$  by  $y_i = \sigma(x_i)$ , the Jacobian matrix is diagonal since  $\partial y_i/\partial x_j = 0$ , if  $i \neq j$ . The Jacobian matrix can be thus flattened into one vector. Accordingly, the matrix multiplication between the Jacobian and  $\overline{\mathbf{y}}$  becomes an element-wise product between two vectors. It is for this reason that Equation (2.4) is optimized to a vector-element-wise product.

- In fully connected layers, every input element x contributes to all output elements during inference; in turn, every x element is influenced by all y elements during gradient computation. In other words, the Jacobian matrix is dense.

The gradient of compounded function can be calculated by chaining VJP calculations. Specifically, Equation (2.3), Equation (2.4) and Equation (2.5) are three VJPs that together calculated the gradient of the function  $\mathcal{L} = \frac{1}{2} \|\mathbf{t} - \sigma(\mathbf{w} \cdot \mathbf{x})\|_2^2$ .

#### 2.2.3.3 Automatic differentiation

Machine learning frameworks typically provide the functionality to compute gradients for any computation graph. The gradients are not calculated using finite difference or symbolic differentiation.

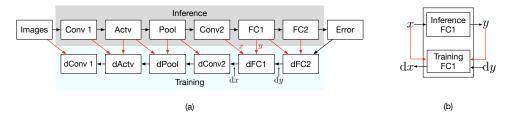

Figure 2.15: AlexNet's forward (on the top) and back propagation (on the bottom). Notice the  $\partial$  sign in front of the layer names in the back propagation stage. The black arrows show the data flow between layers; the red arrows show the data produced in inference and reused in the backpropagation stage.

Rather, the steps for automatic differentiation are generated based on the same rule introduced in §2.2.3.2 and Equation (2.8).

Generically, for any tensor  $\mathbf{x}$ , all of its consumers  $\mathcal{Y}$  in inference contribute to  $\mathbf{x}$ 's gradient during backpropagation. Two values are needed to calculate  $\overline{\mathbf{x}}$  for each consumer  $\mathbf{y}_i \in \mathcal{Y}$ :

- the error gradient  $\overline{\mathbf{y}_i}$ , and

- the Jacobian matrix  $\mathbf{J}_i = \frac{\partial \mathbf{y}_i}{\partial \mathbf{x}}$ . 19

With those values, the gradient of any x in a computation graph can be easily found by

$$\overline{\mathbf{x}} = \sum_i \mathbf{J}_i \cdot \overline{\mathbf{y}_i}, \,\, orall \mathbf{y}_i \in \mathcal{Y}$$

#### 2.2.4 Workload in CNN training

In summary, every layer that participated in inference has to conduct gradient computations and weight updates<sup>20</sup> in backpropagation. Figure 2.15 portrays forward and backpropagation for AlexNet [13], in which arrows depict the directions of data flow.

During forward propagation, layer l will receive input  $\mathbf{x}^{(l)}$  from the previous layer, transforms it with its set of weights  $\mathbf{w}^{(l)}$  and outputs the result  $\mathbf{y}^{(l)}$  to the next layer. In backpropagation, a layer takes  $\overline{\mathbf{y}^{(l+1)}}$  as gradient input and produces  $\overline{\mathbf{x}^{(l)}}$ , whose gradient calculations often require  $\mathbf{w}^{(l)}$ ,  $\mathbf{x}^{(l)}$  and  $\mathbf{y}^{(l)}$ .<sup>21</sup>

#### 2.3 TensorFlow

Google's TensorFlow is one of the most widely adopted machine learning frameworks. It supports a vast range of machine learning models, and it supports the execution of machine learning applications

$<sup>^{19}</sup>$ Machine learning frameworks often have defined the Jacobian matrices for commonly used functions.

$<sup>^{20}</sup>$ Weight update is only required for the layers that use weights.

<sup>&</sup>lt;sup>21</sup>Some types of layers require either  $\mathbf{x}^{(l)}$  or  $\mathbf{y}^{(l)}$ .

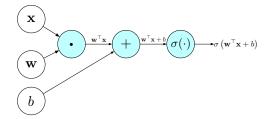

Figure 2.16: Computation graph representing  $\mathbf{y} = \sigma(\mathbf{w}^{\top}\mathbf{x} + b)$ . Dataflow within the graph is represented by the directed edges, math operations are represented by circular nodes. The values shown on the edges are the outputs from the operations. For instance, the  $\odot$  node takes the transposed  $\mathbf{w}$  and  $\mathbf{x}$  and calculates their inner product  $\mathbf{w}^{\top} \cdot \mathbf{x}$ .

on a variety of different types of processors and accelerators (CPU, GPU and TPU) in both local and distributed environments.

TensorFlow, like many other frameworks supporting machine learning such as Torch [5] and MxNet [3], employs direct acyclic graphs (DAGs), called *computation graphs*, to represent computations and dataflow. Figure 2.16 depicts a simple computation graph that represent the calculations of a fully connected layer, namely  $\sigma(y = \mathbf{w}^{\top}\mathbf{x} + b)$ . The n-dimensional data flowing in the computation graph are called *tensors*. For example, a 1D tensor is a vector; a 2D tensor is a matrix. This section presents a background of TensorFlow's local execution environments.<sup>22</sup>

#### 2.3.1 Programming and execution model

The TensorFlow framework contains two major components, a user-facing frontend, called the *client*, and a backend runtime, called the *master*. Users interface with the client to define machine learning models; the client then constructs the computation graphs accordingly. The master is responsible for optimizing, scheduling and running the computation graph on physical processors.

#### Client

The TensorFlow client, available in many programming languages including Python and C, is an interface that machine learning engineers use to create machine learning models by defining the data flow. For example, the TensorFlow API calls in Listing  $2.1^{23}$  implement a typical TensorFlow application performing linear regression, whose computation graph is shown in Figure 2.17. In the first step, the input tensors x and t, and weight tensor w are defined. Next, y is defined as the inner product of x and w, they are used as symbols in creating the computation graph. Loss, gradient calculations and

$<sup>^{22}</sup>$ The distributed runtime of TensorFlow is omitted from the discussion.

$<sup>^{23}\</sup>mathrm{Some}$  APIs in the listing are renamed for better readability.

```

1 # 1. Defining input/output/weights

2 x = tf.input(shape=[BATCH_SIZE, FEATURE_SIZE])

3 t = tf.input(shape=[BATCH_SIZE, OUTPUT_SIZE])

4 w = tf.weight(shape=[FEATURE_SIZE, OUTPUT_SIZE])

5 # 2. Defining inference model

6 y = tf.matmul(w.transpose(), x)

7 # 3. Defining the loss

8 loss = tf.mean_squared_error(y, t)

9 # 4.a. Add gradient calculation steps

10 gradients = tf.gradients(loss)

11 # 4.b. Update weights

12 opt = tf.GradientDescent(learning_rate).apply_gradients(gradients)

13 # Run the model with master

14 with tf.Session(): # opens session with master

15 tf.run(opt)

```

Listing 2.1: Example TensorFlow application

Figure 2.17: The steps involved in building the computation graph from the API calls in Listing 2.1. The step markers at the top of the figure correspond to the step numbers in the comments of the listing.

weight updates are then defined in the next steps. Lastly, the run method is called to invoke the TensorFlow master for execution.

The TensorFlow client is unaware of the implementation details required for graph execution. Instead, the TensorFlow client invokes the master and passes down the computation graph in a text format similar to XML.<sup>24</sup>

#### Master

The master first reconstructs the computation graph passed to it in text format, into its own data format. The master then applies a series of optimizations to the graph, including graph pruning, common expression elimination and constant folding. After the optimization stage, the master starts executing the graph. Execution of the optimized computation graph follows a breadth-first order. More specifically, once a node finishes execution, the scheduler enqueues operations whose inputs are computed and available into the *ready queue*.

$<sup>^{24}</sup>$ The format is called ProtocolBuffer, an interface that serializes structured data [6].

#### 2.3.2 Computation graph

The computation graph is constructed with nodes (or vertices) and edges.

**Nodes** Nodes, also called *operations*, abstract actions that produce or transform tensors in the graph. An operation can take zero or more inputs and produces zero or more outputs. As such, operations can represent arithmetic computations, constants or even data transfers tasks. Particularly in Figure 2.16 the ' $\top$ ' node is a unary operation that transposes its input; and the ' $\cdot$ ' node takes two matrix-inputs and calculates inner product; data nodes like ' $\mathbf{x}$ ' produce data tensors without taking any input.

**Edges** Edges set up producer-consumer relationships between operations. In computation graph speak, tensors are represented by edges.

Using a computation graph allows TensorFlow to decouple data and the computations. That is, the same computation graph is reused multiple times with different data. TensorFlow also supports partial execution so that if the user requests the result of  $\mathbf{w}^{\top}\mathbf{x}$  in Figure 2.16 (the result from the dot node), TensorFlow executes only the subgraph that produces  $\mathbf{w}^{\top}\mathbf{x}$  and will not execute the subgraph that involves the '+' and ' $\sigma$ ' operations.

One key difference between the client and master graphs is that edges in the client graph do not have data storage associated. For example, in Figure 2.16, the buffer storing  $\mathbf{w}^{\top}\mathbf{x}$ , could be used to store  $\mathbf{w}^{\top}\mathbf{x} + b$  and y because they have the same shapes and in turn require the same amount of space. However, the client is unaware of the actual implementation of the math operations (whether they support in-place updates or not), and hence does not concern itself with buffers. It is the backend master that assigns buffers to tensors.

#### 2.3.3 Execution order

Producer-consumer relationships, or more specifically data dependencies, determine execution orders in TensorFlow. For instance, operation A runs before operation B if B requires as input, the data that A produces. Another type of dependency, called *control dependency*, enforces execution order between operations that do not have data dependencies. By setting C as A's control dependency, C is guaranteed to run before A, even if there is no data dependency between them. If the user sets another dependency that requires A to run before C, a dependency cycle is created and TensorFlow will stop and report an error.

#### 2.3.4 GPU support

A specialized TensorFlow interface called StreamExecutor is used for abstracting co-processors like GPUs. All GPU related tasks, such as performing math operations, and copying memory, are requested through this interface. However, StreamExecutor abstracts only a subset of the available GPU functions, such as launching compute kernels or calling device driver functions. Some functions are not natively supported; for instance, cudaMemPrefetchAsync(), a function that is widely used in our work. As a result, we had to modify StreamExecutor to also support the other GPU functions needed to control the virtual memory.

Memory management The TensorFlow runtime allocates all free global memory and manages the memory internally. As such, tensor allocations and deallocations will not invoke high overhead memory control directives like cudaMalloc() and cudaFree(). Tensors are reference counted, such that a tensor can be freed automatically when its last consuming operation finishes.

# Chapter 3

# Design

In the previous sections, we established the following:

- Computation and dataflow of machine learning applications are often represented by computation graphs in machine learning frameworks like TensorFlow.

- Nvidia's virtual memory subsystem on the recent GPU hardware enables running GPU programs that require more memory than what is physically available in global memory.

- Nvidia provides APIs for applications to issue memory management hints to aid the virtual memory subsystem in making virtual memory management decisions such as offloading and prefetching data from and to global memory. This allows the application to issue virtual memory hints based on its knowledge of the workload.

In this chapter, we first define the problem that we try to solve, and then present the specific requirements for supporting machine learning applications. In  $\S 3.2$  we present our design, leading to a new system we call " $Auto\,VM$ ."

#### 3.1 Motivation and Problem Statement

#### Motivation

Training state-of-the-art convolutional neural networks is time intensive. For example, training ResNet-50 [7] on the ImageNet-1K dataset [17] for 90 epochs takes 14 days using a single M40 GPU and takes 29 hours on a machine with eight Nvidia Tesla P100 GPUs [21]. Our goal is to improve training speed by optimizing memory access locality. Improved training speed allows machine learning engineers to apply larger networks to throughput critical applications whose latency requirements would have previously been attainable only by using simpler networks. Furthermore, performance of different neural network structures can be evaluated in a more timely manner, leading to faster time to market.

Training state-of-the-art convolutional neural networks is memory intensive. For example, training Inception v4 [22] with 64-image batches requires over 80GB of memory. Generally, two factors affect the amount of memory needed:

- 1. the complexity of the network, e.g., the more layers the more memory is needed, and

- 2. training batch sizes, i.e., the number of images used in one training iteration.

Using virtual memory in machine learning frameworks allows for more complex networks and larger batch sizes, because virtual memory size can be significantly larger than the amount of physical memory available. Although using virtual memory permits running problems that do not fit in physical memory, the default virtual memory management policy is likely to make suboptimal paging decisions since it is unaware of the running applications' memory access patterns.

Specifically for neural network training, the default memory management policy will tend to make particularly poor paging decisions for problem sets that do not fit in physical global memory, leading to poor response times. For example, in neural network inference, just consumed outputs are rarely referenced again for a prolonged period of time. These outputs are thus ideal candidates for paging out to host memory, but they are not likely to be selected for page-out under the default LRU scheme as they were just referenced.

As a result, the default mechanism does not page out data promptly. Not paging tensors out in a timely way exhausts physical global memory and causes memory thrashing. Furthermore, the default memory management policy cannot predict the data requirements of the subsequent computations.

Consequently, if those operations' operands were previously paged out, they will be demand-paged in, page-by-page, as they are being accessed, decreasing memory throughput.

It is perhaps for this reason that virtual memory is rarely used in frameworks like TensorFlow and Torch. In fact these frameworks make it exceedingly difficult to exploit virtual memory. In the case of TensorFlow, for example, parameter per\_gpu\_memory\_fraction is typically set to below one by machine learning programmers to limit the amount of global memory used. If set to a number higher than one, TensorFlow would use virtual memory. Interestingly, no publicly available document reveals this behaviour. In practice, a bug in TensorFlow r1.14 prevents the users from using virtual memory even if per\_gpu\_memory\_fraction was set correctly.

#### Problem statement

We aimed to design a software layer, AutoVM, that interfaces with the Nvidia driver and machine learning frameworks, that allows for faster training and more complex network structures, by optimizing memory locality when virtual memory is used.

#### Requirements

Our mechanism AutoVM must:

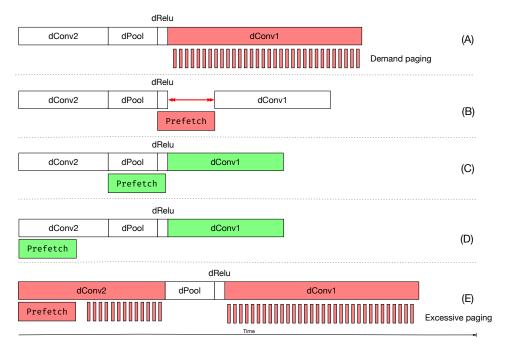

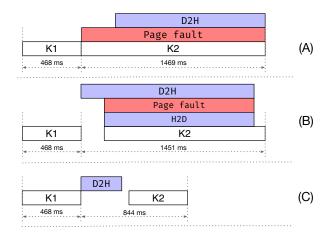

- work within machine learning frameworks like TensorFlow; and